Verilog Block Statements

The block statements are the grouping of two or more statements together, which act syntactically like a single statement. There are two types of blocks in the Verilog:

- Sequential block

- Parallel block

These blocks can be used if more than one statement should be executed. All statements in the sequential blocks will be executed sequentially in the given order.

If a timing control statement appears within a block, then the next statement will be executed after that delay. The sequential block shall be delimited by the keywords begin and end.

All statements in the parallel blocks are executed at the same time or concurrently. It means that the next statement’s execution will not be delayed even if the previous statement contains a timing control statement. The parallel block shall be delimited by the keywords fork and join.

Sequential Block

Statements are wrapped using begin and end keywords and executed sequentially in the given order. Delay values are treated relative to the time of execution of the previous statement.

After all the statements within the block are executed, control may be passed to some other place.

Syntax

Sequential block statement follows the following syntax:

Characteristics

The sequential block has the following characteristics, such as:

- Statements will be executed in the sequence, one after another.

- Delay values for each statement are treated relative to the simulation time of the previous statement’s execution.

- Control can pass out of the block after the last statement executes.

Example

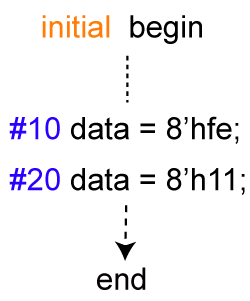

In the above example, first statement in begin and end block will be executed at 10 time units, and the second statement at 30 time units because of the relative nature. It is 20 time units after execution of the previous statement.

Parallel Block

A parallel block can execute statements concurrently, and delay control can be used to provide the assignments’ time-ordering. Statements are launched in parallel by wrapping them within the fork and join keywords.

Syntax

The parallel block has the following simplified syntax:

Characteristics

A parallel block has the following characteristics:

- Statements will execute concurrently.

- Delay values for each statement are considered relative to the simulation time of entering the block.

- Delay control can be used to provide time-ordering for assignments.

- Control can pass out of the block when the last time-ordered statement executes.

Example

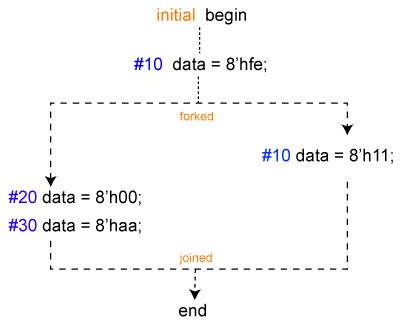

In the above example, fork and join block will be launched after executing the statement at 10-time units.

Statements within this block will be executed in parallel, and the first statement will be the one where data is assigned a value of 8’h00 since the delay for that is 10-time units after the fork-join launch.

After 10 more time units, the first statement will be launched and data will get the value 8’h11.

There is a begin-end block in the above example, and all statements within the begin-end block will be executed sequentially. Still, the block itself will be launched in parallel, along with the other statements. Data will get 8’h11 at 20-time units, 8’h00 at 30-time units, and 8’haa at 60-time units.

Naming of blocks

Both sequential and parallel blocks can be named by adding name_of_block after the begin and fork keywords. By doing this, the block can be referenced in a disable statement.